# Relationships between communication models based on registers for fault-tolerant distributed computing on networks

Colette Johnen, Lisa Higham Univ. Bordeaux, CNRS, LaBRI, UMR 5800

## Semantics of a register [Lamport 86]

#### Single-Writer Register (SR)- def

- A <u>register</u> is a memory cell on which two types of operations are possible **READ** and **WRITE**

- On a <u>Single-Writer register</u>, only one process can do the WRITE operation

- On a register R, READ and WRITE operation are not atomic, they take some time

A **READ** operation on a register *R* may overlap several **WRITE** operations on *R*

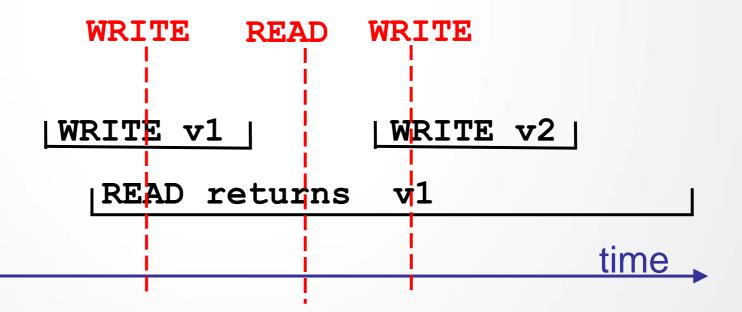

#### Single-Writer register - semantic

On R, a READ operation that does not overlap any WRITE operation returns the most recent preceding written value (v1) in R

time

WRITE value v1 | READ returns v1

#### Safe register [Lamport 86]

On R, a READ operation that does overlap a WRITE operation may return any value

### Regular and Atomic register [Lamport 86]

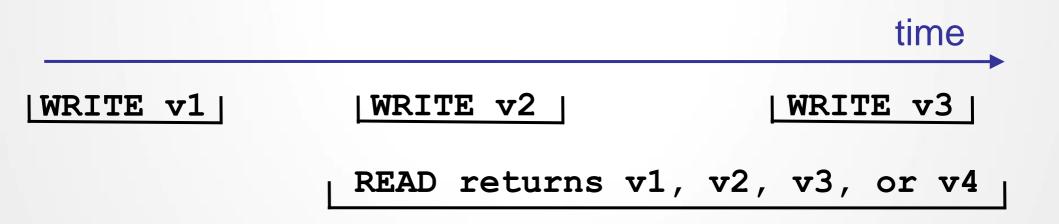

On R, a READ operation that does overlap a WRITE

operation returns the most recent preceding written value

or any value written during overlapping WRITE operations

```

WRITE v1 WRITE v2 WRITE v3

[READ returns v1, v2, or v3]

[READ returns v1 or v2]

```

6

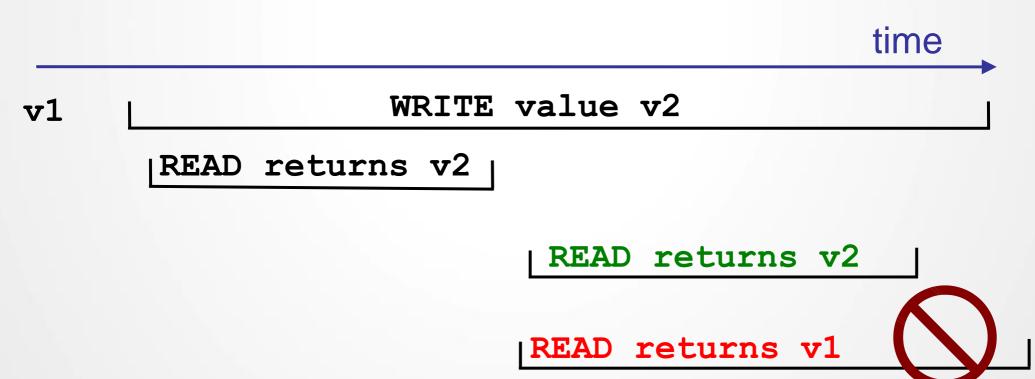

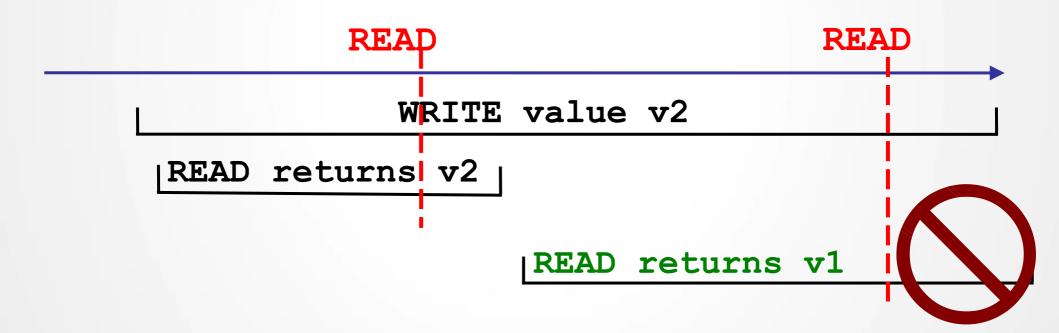

#### Atomic register [Lamport 86]

On R, if a READ operation returns the value written during the overlapping WRITE operation then any subsequence READ cannot return the most recent preceding written value (v1)

#### Property of <u>atomic</u> registers

A sequence of operations on an atomic register is linearizable [Herlihy, Wing 90]

Each operation appears to happen instantaneously at some point during its execution

#### Regular register

A sequence of operations on an regular register may not linearizable

9

#### Communication Model on networks

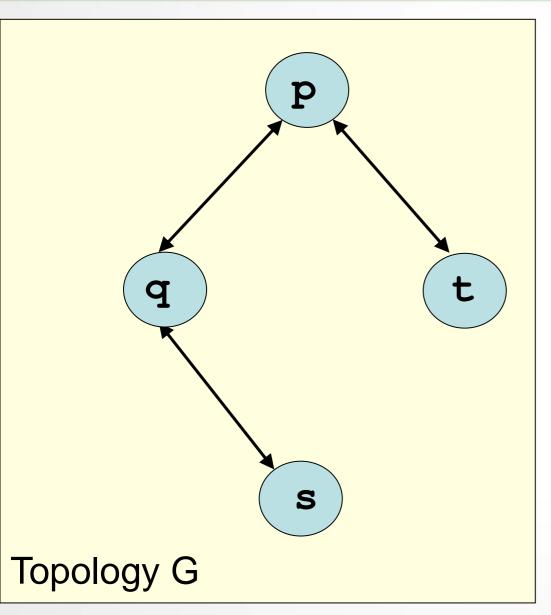

#### Distributed computing on networks

A processor can only communicate with its neighbors

Ex: p can only communicate with q and t

### Communication modelS based on Single-Writer registers

a single register per process : multi-reader register

[MN98], [AS99], [H00], [NA02]

a register is associated to a link: single-reader register

[DIM93], [Dolev 02]

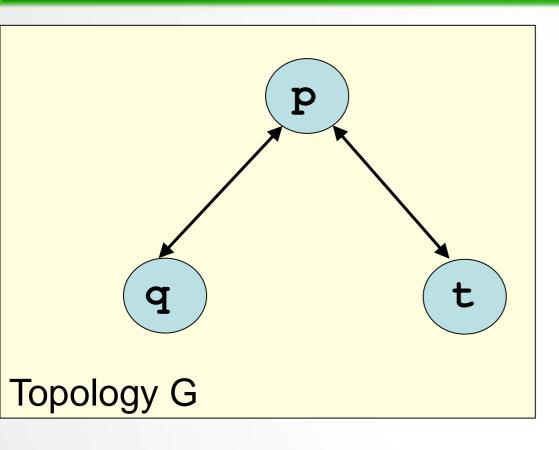

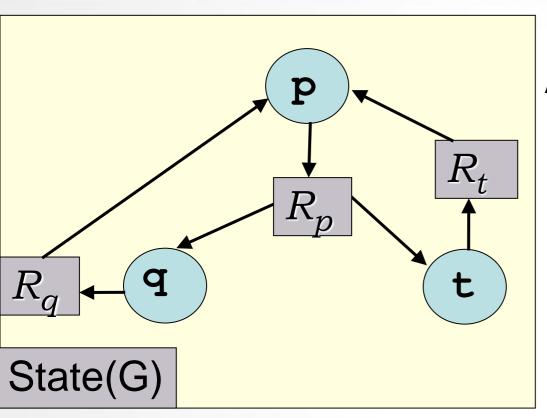

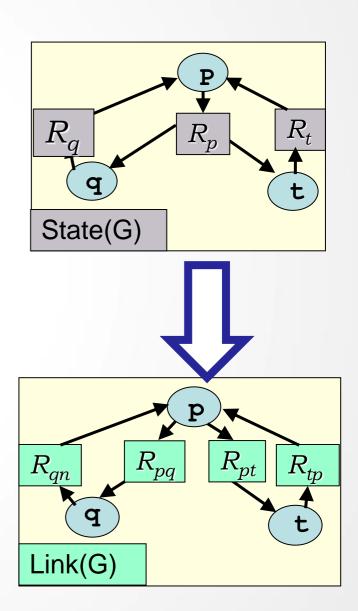

### a single register per process: state network model

A processor p has a single atomic single-writer multireader register  $R_p$

$R_p$  is readable by p's neighbors : q and t

$R_p$  is writable by p

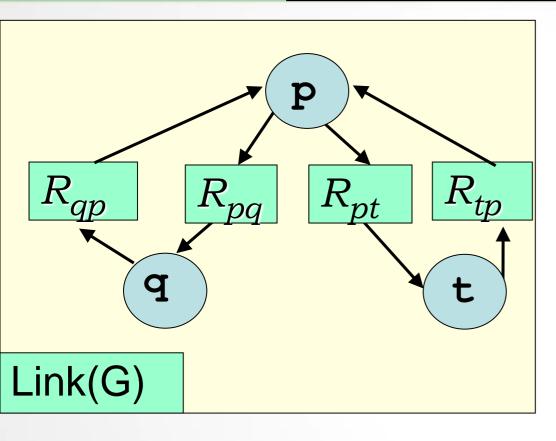

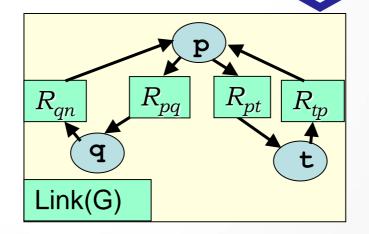

#### Communication model for network: link network model

A processor *p* has several atomic <u>single-writer</u> <u>single-reader</u> registers (one per neighbor)

$R_{pt}$  is readable by t

$R_{pt}$  is writable by p

### Communication models based on registers on network G

| Semantic                   | Atomic                                              | Regular              | Safe              |

|----------------------------|-----------------------------------------------------|----------------------|-------------------|

| location                   |                                                     |                      |                   |

| State<br>multi-reader      | atomic-state(G)<br>[MN98], [AS99], [H00],<br>[NA02] | regular-<br>state(G) | safe-<br>state(G) |

| Link<br>singler-<br>reader | atomic-link(G) Read-Write atomicity model           | regular-<br>link(G)  | safe-<br>link(G)  |

|                            | [DIM93], [Dolev 02]                                 |                      |                   |

#### Distributed System

S = (G : Graph, MC : Communication Model, A : Algo)

Computation of S is the set of computations of A on MC(G)

Goal: to implement every algorithm A for MC1(G) on MC2(G)

16

#### Transformation $\tau : MC1(G) \rightarrow MC2(G)$

Let R be a register of MC1(G) writable by p and readable by qTransformation  $\tau$  is two programs  $\tau(\text{READ}(R))$  returns a value  $\tau(\text{WRITE}(R, v))$

These two programs are a series of **valid READ** and **WRITE** operations on <u>registers of MC2(G)</u>

$\tau(\text{WRITE}(R, v))$  invocation by p contains only READ and WRITE operations on registers respectively readable or writable by p

$\tau(READ(R))$  invocation by q contains only READ and WRITE operations on registers respectively readable or writable bq

#### Simple Transformation State → Link

```

\begin{array}{c} \tau(\textbf{STATE-READ}(R_q)) \\ v \leftarrow \textbf{LINK-READ}(R_{qp}) \\ \text{return } v \end{array}

```

#### Transformation $\tau : MC1(G) \rightarrow MC2(G)$

```

Transformation \tau is two programs \tau(\text{READ}(R)) returns a value \tau(\text{WRITE}(R, \nu))

```

These two programs are a series of **valid READ** and **WRITE** operations on <u>registers of MC2(G)</u>

Let A be an algorithm on MC1(G)  $\tau(A)$ : READ(R) and WRITE(R,  $\nu$ ) operation invocations in A are respectively replaced by two program executions  $\tau(READ(R))$  and  $\tau(WRITE(R, \nu))$

$\tau(A)$  is an algorithm on MC2(G)

#### Compiler $\tau : MC1(G) \rightarrow MC2(G)$

τ be a transformation of MC1(G) to MC2(G)  $\tau$  S1=(G, MC1, A)  $\rightarrow$  S2=(G, M**C2**,  $\tau$ (A))

$\tau(A)$ : READ(R) and WRITE(R,  $\nu$ ) operation invocations in A are respectively replaced by two program executions  $\tau(\text{READ}(R))$  and  $\tau(\text{WRITE}(R, \nu))$

$\tau(A)$  is an algorithm on MC2(G)

The transformation  $\tau$  is a compiler iff S2=(G, MC2,  $\tau(A)$ ) is a syntactically and semantically valid transformation of S1 = (G, MC1, A)

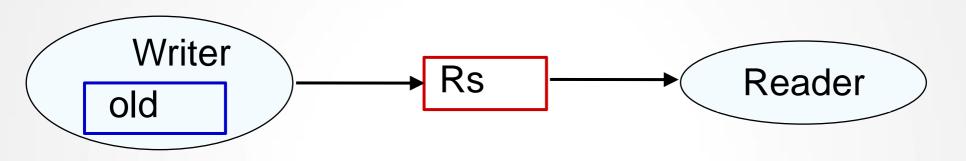

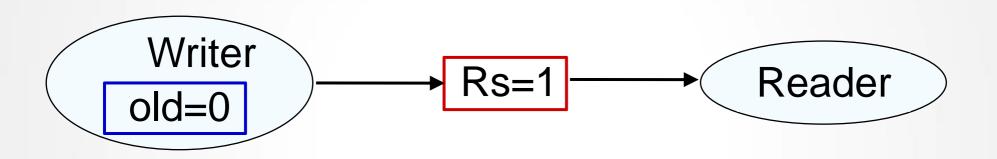

# Wait-free implementation of binary regular SWSR register by a binary safe SWSR register [Lamport 86]

```

t(REG-WRITE(R,new))

if old ≠ new then

SAFE-WRITE(Rs,new))

old ← new;

fi

```

#### Fault tolerance: Wait-Freedom

Wait-free operation: a processor can complete the operation in a finite number of steps, regardless of the actions of other processors

(i.e. a **READ** and a **WRITE** operation is done in finite number of steps)

A wait-free operation is tolerant of processor crashes

a compiler is wait-free if it preserves the wait-freedom property

#### Fault-tolerance: Self-Stabilization

Self-stabilization system automatically convergence to a legitimate configuration from any arbitrary configuration.

From a legitimate configuration, the system behaves correctly (i.e. semantic of READ and WRITE operations is provided).

A self-stabilizing system is tolerant of transient failures that corrupt the processor state.

a compiler is self-stabilizing if it preserves the self-stabilizing property

# Wait-free implementation of binary regular SWSR register by a binary safe SWSR register [Lamport 86]

All reads of the following execution return 1: [(regular-write(R,0), regular-read(R)]\*

Lamport construction is not self-stabilizing

#### Self-stabilizing, Wait-free implementation of SWSR regular binary register by a dual-reader safe binary register [Hoepman, Papatriantafilou, Tsigas 02]

```

τ(REG-WRITE(R,new))

```

```

if SAFE-READ(Rs)≠ new

then

SAFE-WRITE(Rs,new))

fi

```

$\tau$  (REG-READ (R))

SAFE-READ (Rs)

#### Simple Transformation State → Link

$\begin{array}{c} \tau(\texttt{STATE-READ}(R_q)) \\ v \leftarrow \texttt{LINK-READ}(R_{qp}) \\ \text{return } v \end{array}$

ATOMIC-LINK-WRITE ( $R_{pq}$ )  $\tau \text{ (ATOMIC-STATE-WRITE (}R_p, v2 ))$

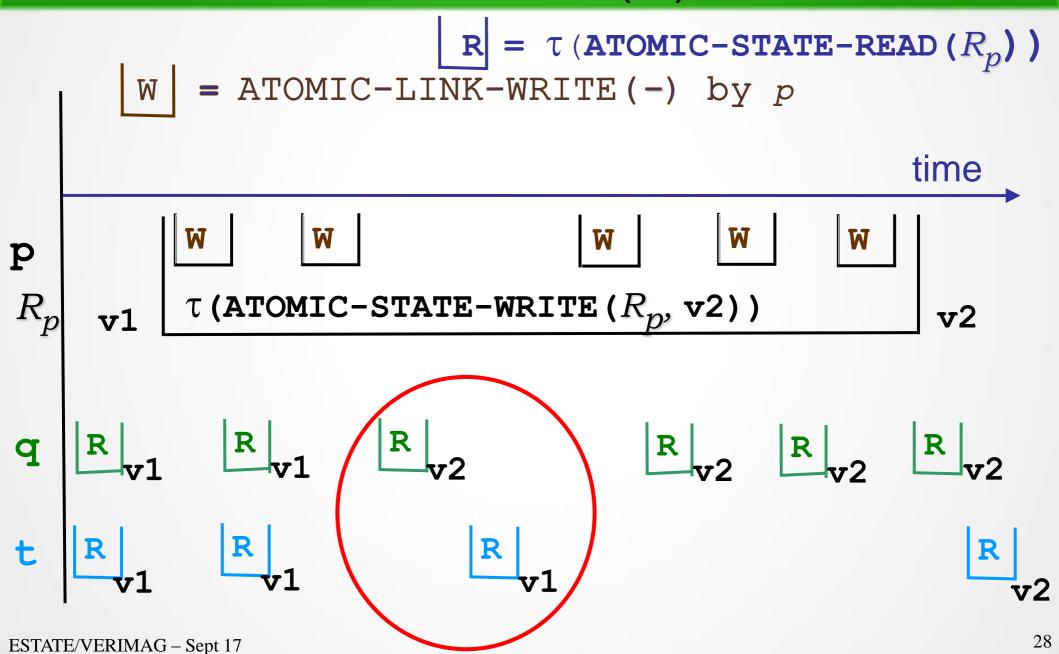

### Linearization of an execution of simple transformation on atomic registers?

$R = \tau (ATOMIC-STATE-READ(R_p))$ Operations on  $R_n$ time WRITE  $(R_{pq}, v2)$  WRITE  $(R_{pt}, v2)$   $\tau$  (ATOMIC-STATE-WRITE  $(R_p, v2)$ )

27

### Wait-Free compiler Atomic-State(G) → Atomic-Link(G) ? NO

#### Wait-free compilers

|                     | Atomic          | Regular         | Safe            |

|---------------------|-----------------|-----------------|-----------------|

| State multi- reader | Higham, Higham, | Johnen 07       |                 |

| Link Single reader  | Johnen 06       | Lamport<br>1986 | Lamport<br>1986 |

29

#### Self-stabilizing compilers

|                      | Atomic                  | Regular   | Safe |

|----------------------|-------------------------|-----------|------|

| State  Multi- reader | C. Johnen, L.           | Higham 07 |      |

| Link Single reader   | L. Higham, C. Johnen 06 |           |      |

30

### Self-Stabilizing compiler Atomic-State(G) → Atomic-Link(G) [IPDPS06]

Drawbacks/Features of Self-Stabilizing compiler from Atomic-State(G) to Atomic-Link(G) [IPDPS06]:

- $\tau(\texttt{ATOMIC-STATE-WRITE}(R_p))$  is not wait-free : during an execution of  $\tau(\texttt{ATOMIC-STATE-WRITE}(R_p))$  any p's neighbor, q, has to do the operation  $\texttt{ATOMIC-LINK-READ}(R_{pq})$  two times

- Each process performs infinitely often ATOMIC-STATE-READ operations

- $\tau(ATOMIC-STATE-READ(R_p))$  )) is not wait-free

### Self-Stabilizing compiler Atomic-State(G) → Regular-State(G)

Drawbacks/Features of compiler from Atomic-State(G) of Regular-State(G) :

- $\tau(ATOMIC-STATE-WRITE(R_p))$  is wait-free

- $\tau(\texttt{ATOMIC-STATE-READ}(R_p))$  is not wait-free in case there is an overlay  $\tau(\texttt{ATOMIC-STATE-WRITE}\ (R_p))$

• Each process p performs one  $\tau(ATOMIC-STATE-WRITE (R_p))$  operation

#### Wait-free and Self-stabilizing compilers

|                  | Atomic              | Regular                  | Safe      |

|------------------|---------------------|--------------------------|-----------|

| State            |                     | Simple<br>transformation |           |

| multi-<br>reader |                     |                          |           |

| Link             |                     | Johnen,                  | Higham 09 |

| Single reader    | «Lampoi<br>Conjectu |                          |           |

33

#### Bibliography

Self-stabilizing algorithms in ATOMIC-LINK network model:

[DIM93], [Dolev 02] called R/W atomicity model

• Self-stabilizing algorithms in ATOMIC-STATE network model :

[MN98], [AS99], [H00], [NA02]

#### compilerAtomic-state to Atomic-link

#### A register has 4 fields:

- written value and written flag

- copied value and copied flag

#### Definition of atomic-Link procedures

**Read**  $R_{xy}$  (wv, wf, cv, cf): an atomic-link-read( $R_{xy}$ ) operation retuning: w\_v, w\_f, c\_v, c\_f

Write  $R_{xy}$  (wv, wf, cv, cf) : an atomic-link-write  $(R_{xy})$  operation to write w\_v, w\_f, c\_v, c\_f

Acknowledged-writing in  $R_{xy}$  of (v, f) - by x:

Write

$$R_{xy}$$

Read  $R_{xy}$   $(\mathbf{v}, \mathbf{f}, -, -)$

Acknowledged-reading in  $R_{xy}$  of (v, f) - by x:

Read

$$R_{xy}$$

Write  $R_{xy}$  (v, f, -, -)  $\left| (-, -, v, f) \right|$

#### τ(ATOMIC-STATE-WRITE(-,-))

Procedures on  $R_{tp}$  during a  $\tau$  (ATOMIC-STATE-WRITE ( $R_t$ , v2))

#### By t:

```

acknowledged-writing acknowledged-writing in R_{tp} of (v2, 0) in R_{tp} of (v2, 1)

```

$\tau$  (ATOMIC-STATE-WRITE ( $R_t$ , v2))

#### By p:

acknowledgedreading in  $R_{pt}$  of (v2, 0) acknowledgedreading in  $R_{pt}$  of (v2, 1)

#### T(ATOMIC-STATE-WRITE(-,-))

Procedures on  $R_{pt}$  or  $R_{pq}$  during a  $\tau$  (ATOMIC-STATE-WRITE ( $R_p$ , -))

**A-W** in  $R_{px}$  of (v, f) : an acknowledged-writing in  $R_{px}$  of (v, f) - by p

#### $\tau(\texttt{ATOMIC-STATE-READ}(R_x))$ by y

Procedures on  $R_{xy}$  during a  $\tau$  (ATOMIC-STATE-READ ( $R_x$ )) by  $\mathbf{y}$

By y:

A-R in

$$R_{xy}$$

of  $(-, 0)$  A-R in  $R_{xy}$  of  $(-, 0)$  of  $(-, 0)$

A-R in  $R_{xy}$  of (v, f): an acknowledged-reading  $(\mathbf{R}_{xy})$  returning (v, f)

August 2006 40

#### No wait-free compiler on network

Let G be a network topology that is not complete

Theorem: there is not wait-free compiler from AS(G) to AL(G)

IPDPS'06

August 2006 42

### 1-Regular [Abraham, Chockler, Keidar, Malkhi 07]

On *R*, a **READ** operation that <u>does</u> overlap a <u>single</u> **WRITE** operation returns the most recent preceding written value (v1) <u>or the</u> value written during <u>the</u> overlapping **WRITE** operations (v2)

```

WRITE v1 WRITE v2 WRITE v3

READ returns v1, v2, v3, or v4

READ returns v1 or v2

```